Erstellung eines cRio

Modul für die NI cRIO(-9022 / Chassis 9114)

Eigenschaften :

- keine Scanengine Unterstützung

- Einbindung nur in der FPGA Ebene

- Nutzung vorhandener Treiber z.B. NI 9401

- keine Galvanischetrennung vom Messsystem

- AD- Wandler (MCP3002)

- 1-Kanal

- 10 Bit Auflösung

- 200 kHz

- max. Messspannung 5V

- keine Scanengine Unterstützung

- Einbindung nur in der FPGA Ebene

- Nutzung vorhandener Treiber z.B. NI 9401

- keine Galvanischetrennung vom Messsystem

- AD- Wandler (MCP3002)

- 1-Kanal

- 10 Bit Auflösung

- 200 kHz

- max. Messspannung 5V

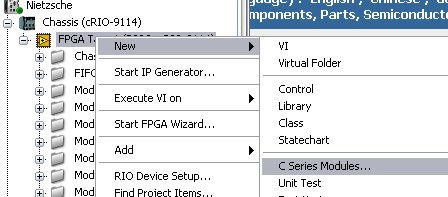

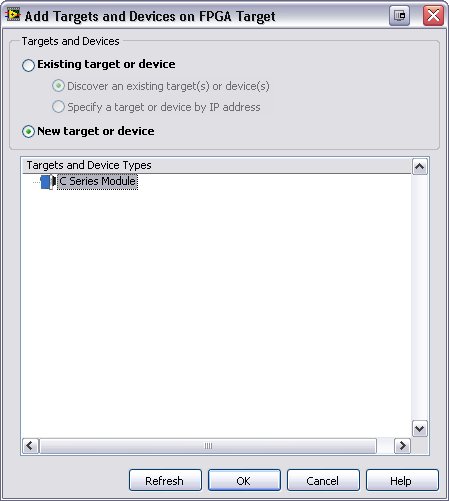

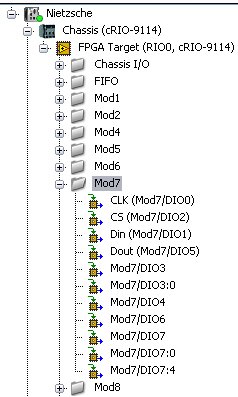

Um ein Modul verfügbar im Chassis der cRio zu machen benötigt man einen kleinen Trick, da diese nach den Modulen selbst scannen kann und das Modul so nicht findet oder erkennt. Über Chassis -> FPGATarget -> New -> C Series Modules...

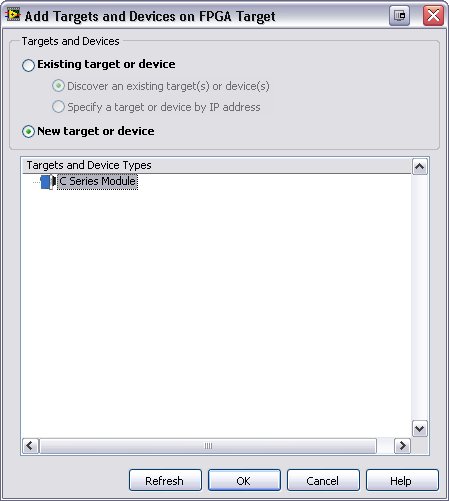

danach weiter

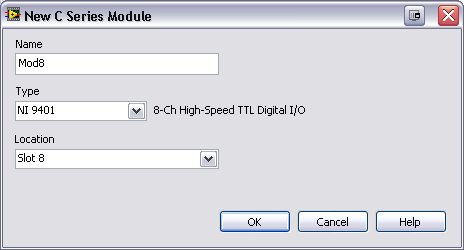

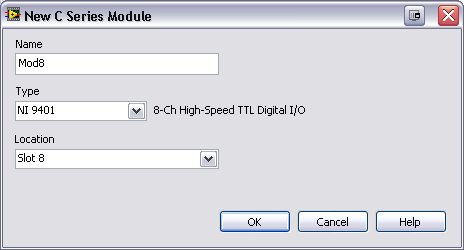

Nun hat man die "freie" Auswahl an Modulen. Hier im Beispiel ist nur noch Slot 8 frei und der Type wird für das Modul NI 9401 das 8-CH High-Speed TTL Digital I/O eingestellt.

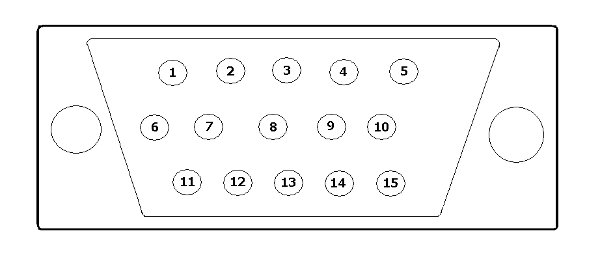

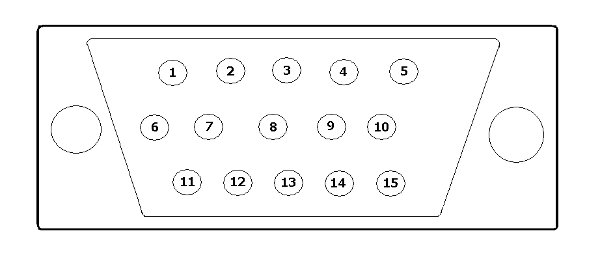

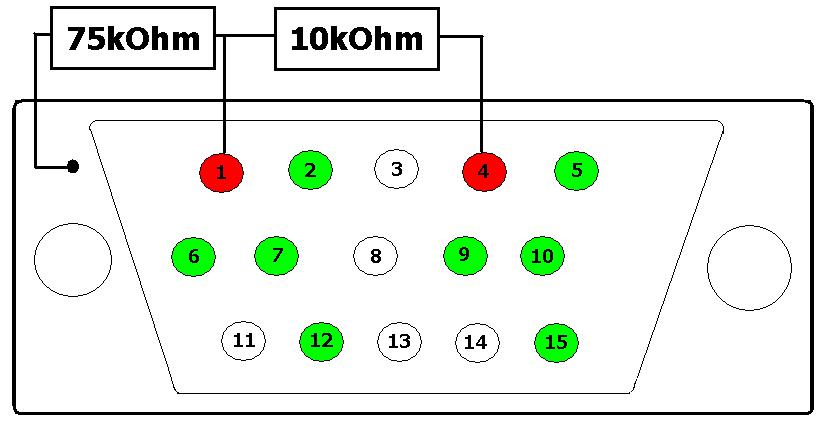

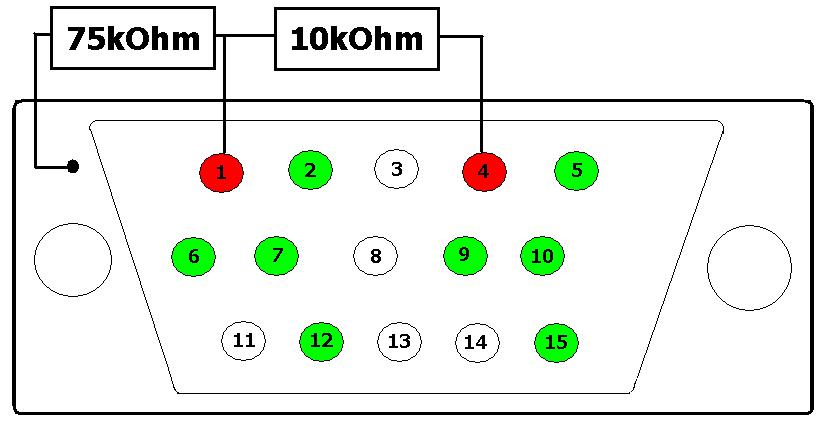

(Lötseite Buchse!)

Nun hat man die "freie" Auswahl an Modulen. Hier im Beispiel ist nur noch Slot 8 frei und der Type wird für das Modul NI 9401 das 8-CH High-Speed TTL Digital I/O eingestellt.

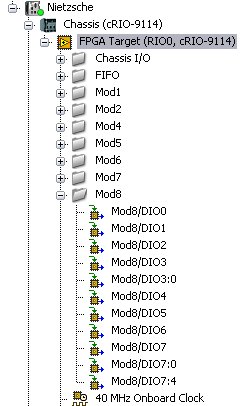

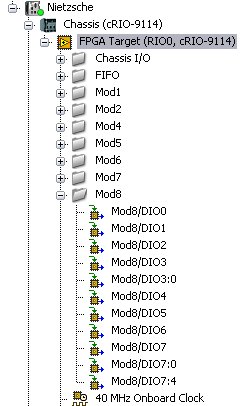

Nach

dieser Einstellung

erscheint das Modul im Projektexplorer.

Natürlich ist

das Modul nicht real vorhanden und außerdem soll auch ein

Modul mit einem Kanal zur Spannungsmessung erstellt werden. Das

Prinzip ist einfach, die cRio arbeitet mit einem NI 9401 Modul welches

keines ist und der Anwender hat sein eigenes Modul, muss allerdings

darauf achten, dass er es so programmiert, dass dieses sich wie ein NI

9401 Modul verhält.

(Lötseite Buchse!)

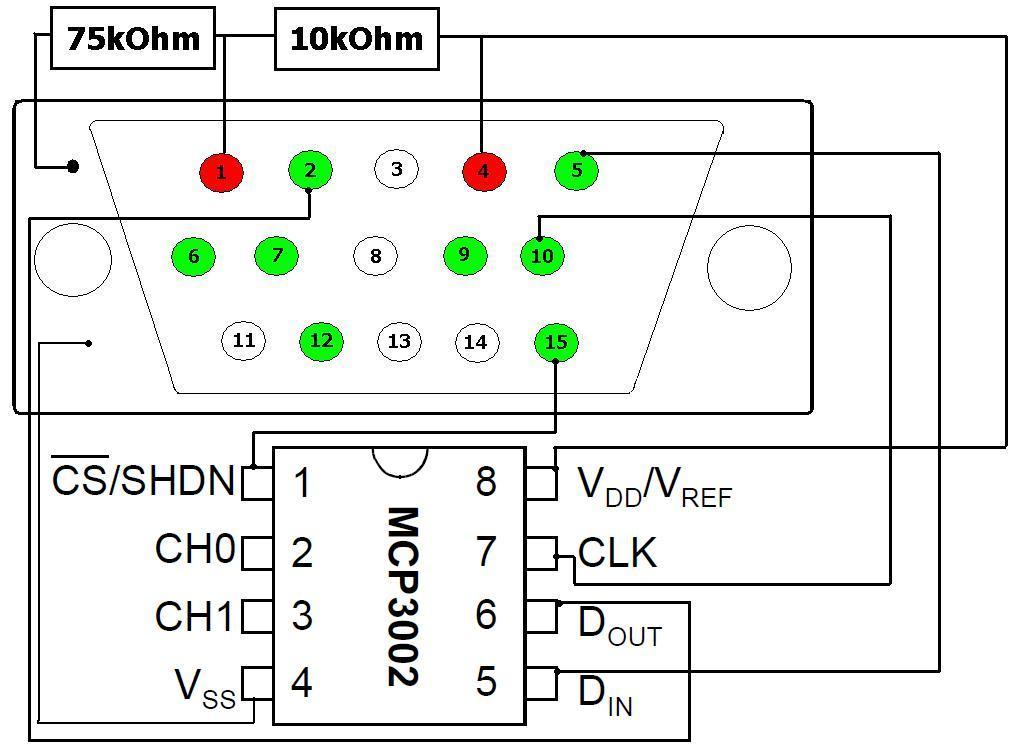

Das

Chassis

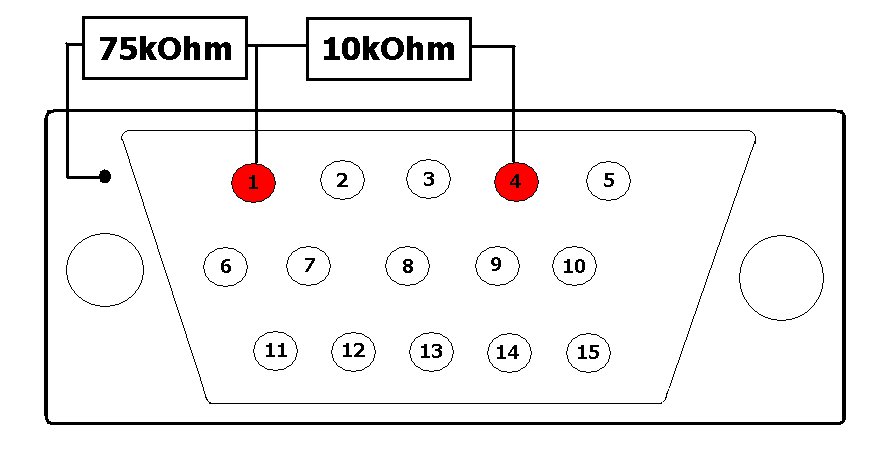

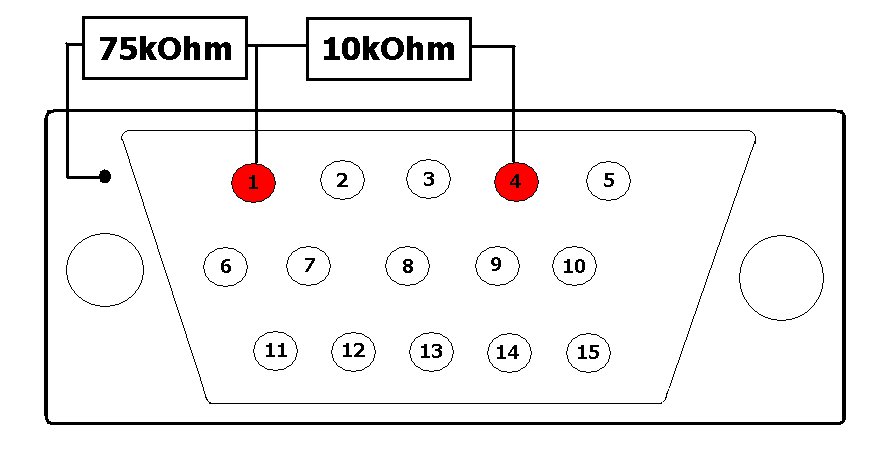

hat hier 8 Slots und jeder Slot hat einen 15 poligen Stecker.

Pin 4 ist von dem Chassis aus unser Vcc von 5V, der GND wird

über das Gehäuse hergestellt. Nun verbindet man Pin 4

über einen 10kOhm Widerstand mit dem Pin 1 und von Pin 1

über einen 75kOhm Widerstand zum Gehäuse.

Nach dieser

Beschaltung

kann man das Modul in den Code einbinden und ist nun in der Lage 8 I/Os

zu schalten. Das Chassis "glaubt" ein NI 9401 Modul sitzt im Slot 8.

Mit Schalten ist gemeint, sind z.B. die ersten 4 I/Os als

Ausgänge definiert und man schaltet Mod8/DIO0 im Programm,

aktiviert sich im Chassis im Slot 8 der Pin 10 von 0V auf ca. 3,2V. Ist

Mod8/DIO0 als Eingang definiert, so ließt dieser das

TTL-Signal an Pin 10 aus.

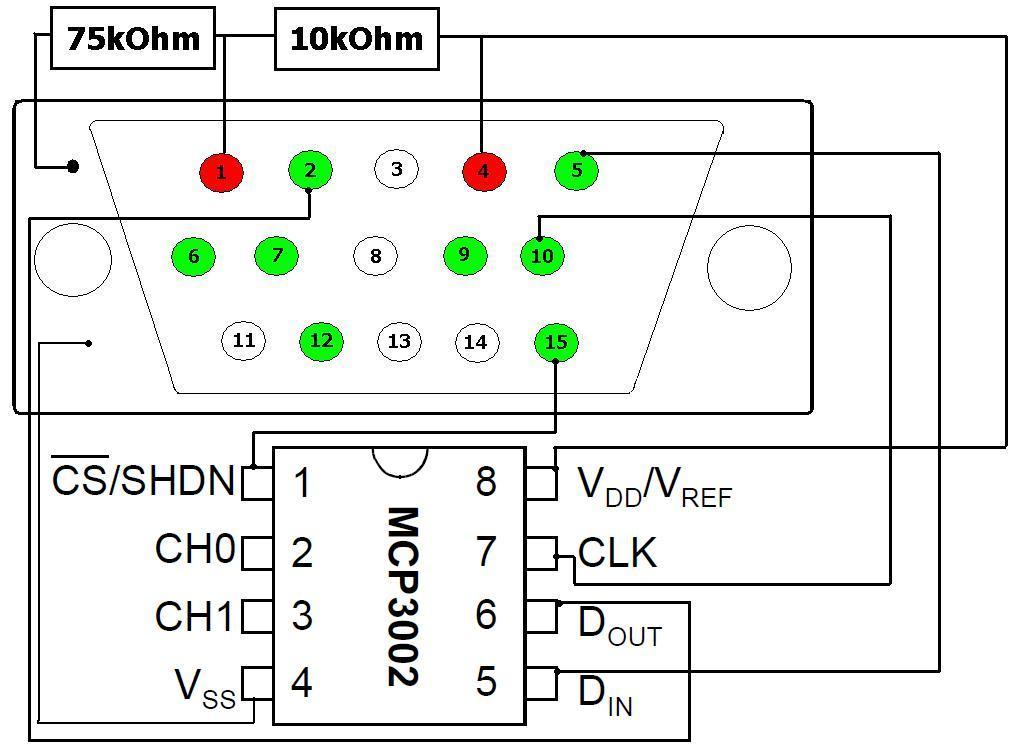

Je nach Konfiguration des Moduls hat man entweder 8 Ausgänge, 8 Eingänge oder 4 Ausgänge und 4 Eingänge. Für dem MCP3002 dem AD Wandler brauchen wir 3 Ausgänge und 1 Eingang. Somit wird der letzte Konfigurationszustand für das Modul gewählt.

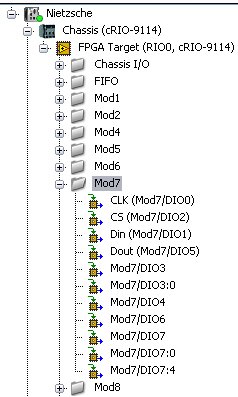

Der AD Wandler ist jetzt auf Slot 7! DIO0 = CLK (Ausgang), DI01 = Din (Ausgang), DIO2 = CS (Ausgang) und DIO5 = Dout (Eingang). Das Interessante ist natürlich an welchem Pin nun der jeweilige Programmierte Aus-/ Eingang liegt.

Je nach Konfiguration des Moduls hat man entweder 8 Ausgänge, 8 Eingänge oder 4 Ausgänge und 4 Eingänge. Für dem MCP3002 dem AD Wandler brauchen wir 3 Ausgänge und 1 Eingang. Somit wird der letzte Konfigurationszustand für das Modul gewählt.

Sieht man sich das

Kommunikationsprotokoll des MCP3002 an, gibt es

insgesamt 4 Signale. Drei Steuersignale und einen Ausgangssignal (Seite

14). CS für Channel Select, CLK für Clock, Din für die

Kommunikation von cRio zum AD Wandler und Dout vom AD Wandler zur cRio.

Desweiteren ist der Verbauch des ICs so gering, dass man dieses

von dem Chassis versorgen lassen kann, über Pin 4 (Vcc = 5V).

Um die Signale richtig zu programmieren muss man das Datenblatt genau studieren. Das CS ist erstmal irrelevant (da es nur den Start der Kommunikation einleitet). CLK ist f_CLK=16*f_Sample (Abtastrate = f_Sample = 200kHz) => CLK sollte eine Frequenz von 3,2MHz (bei Vcc= 5V) haben und Din ist eher uninteressant, da die Konfigurationen des AD Wandlers konstant sein sollen und Dout wird wiederum nur eingelesen.

Es ist nun aber auch nichts anderes zu tun, als das Kommunikationsdiagramm von Seite 14 (FIGURE 5-1) logisch einzuprogrammieren.

Um die Signale richtig zu programmieren muss man das Datenblatt genau studieren. Das CS ist erstmal irrelevant (da es nur den Start der Kommunikation einleitet). CLK ist f_CLK=16*f_Sample (Abtastrate = f_Sample = 200kHz) => CLK sollte eine Frequenz von 3,2MHz (bei Vcc= 5V) haben und Din ist eher uninteressant, da die Konfigurationen des AD Wandlers konstant sein sollen und Dout wird wiederum nur eingelesen.

Es ist nun aber auch nichts anderes zu tun, als das Kommunikationsdiagramm von Seite 14 (FIGURE 5-1) logisch einzuprogrammieren.

Der AD Wandler ist jetzt auf Slot 7! DIO0 = CLK (Ausgang), DI01 = Din (Ausgang), DIO2 = CS (Ausgang) und DIO5 = Dout (Eingang). Das Interessante ist natürlich an welchem Pin nun der jeweilige Programmierte Aus-/ Eingang liegt.

DIO0 = Pin 10

DIO1 = Pin 5

DIO2 = Pin 15

DIO3 = Pin 9

DIO4 = Pin 7

DIO5 = Pin 2

DIO6 = Pin 12

DIO7 = Pin 6

DIO1 = Pin 5

DIO2 = Pin 15

DIO3 = Pin 9

DIO4 = Pin 7

DIO5 = Pin 2

DIO6 = Pin 12

DIO7 = Pin 6

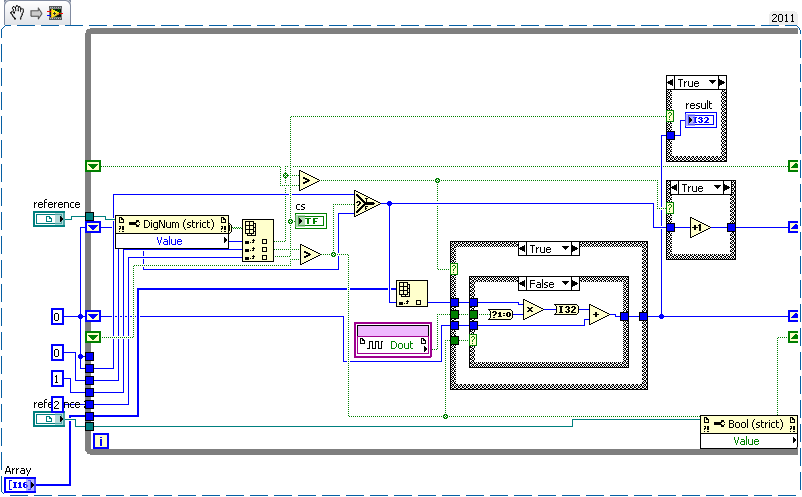

Ist

die Schaltung aufgebaut, ist es nun möglichdie einzelne

Ausgänge zu schalten, der Eingang DIO5 ist vorerst

uninteressant, da der MCP3002 erst eine korrekte Kommunikation braucht

ehe er antwortet. Es macht natürlich keinen Sinn DIO0 bis DIO2 mit

Programm-Schaltern zu versehen und diese manuell zuschalten. Allerdings

reicht dies aus, um zu prüfen ob alles richtig aufgebaut wurde.

CS wird nur bei Kommunikationsbeginn von High auf Low geschaltet, die CLK liefert die Taktfrequenz und muss abwechselnd von High auf Low geschaltet werden. Abschließend muss Din am Anfang der Kommunikation speziell eingestellt werden, hier gebe ich High, High, Low, High vor! (Das bedeutet: Start, Single Channel, Kanal 0, höherwertiges Bit zuerst)

Also ist klar während einer kompletten Kommunikation muss CS 2mal auf High, CLK 16 mal auf Low und 16 mal auf High, Din 3mal auf High und einmal auf Low geschaltet werden. Um es einfach zu halten, erstellt man ein Array Typ Bool mit einer Indexgröße von 38, da CLK 38 mal geschaltet werden muss, ebenso müssen die Signale für die CS und Din über diese Größe definiert sein.

Dies entspricht nun dem CLK Signal aus der FIGURE 5-1 auf Seite 14 vom Datenblatt MCP3002, folglich ergibt sich daraus für Din :

Worauf

geachtet werden muss ist das die Pegel von Din oder CS über eine

Periode von CLK dauern müssen, damit der MCP3002 die Signale

versteht, für CS :

CS wird nur bei Kommunikationsbeginn von High auf Low geschaltet, die CLK liefert die Taktfrequenz und muss abwechselnd von High auf Low geschaltet werden. Abschließend muss Din am Anfang der Kommunikation speziell eingestellt werden, hier gebe ich High, High, Low, High vor! (Das bedeutet: Start, Single Channel, Kanal 0, höherwertiges Bit zuerst)

Also ist klar während einer kompletten Kommunikation muss CS 2mal auf High, CLK 16 mal auf Low und 16 mal auf High, Din 3mal auf High und einmal auf Low geschaltet werden. Um es einfach zu halten, erstellt man ein Array Typ Bool mit einer Indexgröße von 38, da CLK 38 mal geschaltet werden muss, ebenso müssen die Signale für die CS und Din über diese Größe definiert sein.

Dies entspricht nun dem CLK Signal aus der FIGURE 5-1 auf Seite 14 vom Datenblatt MCP3002, folglich ergibt sich daraus für Din :

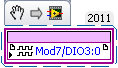

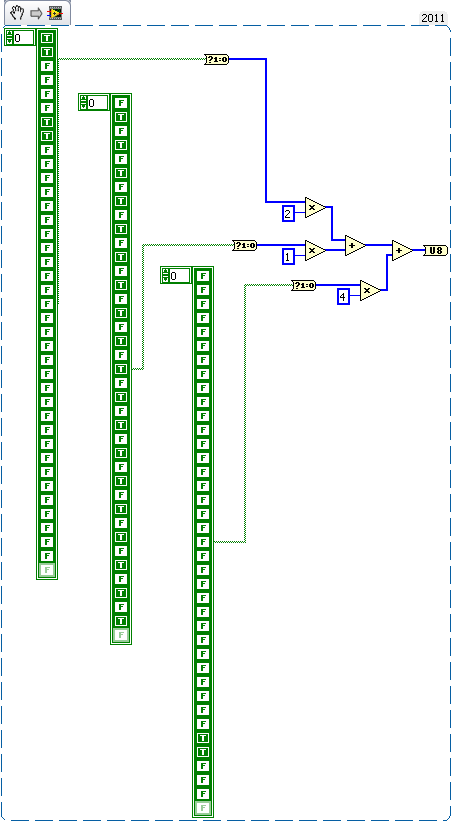

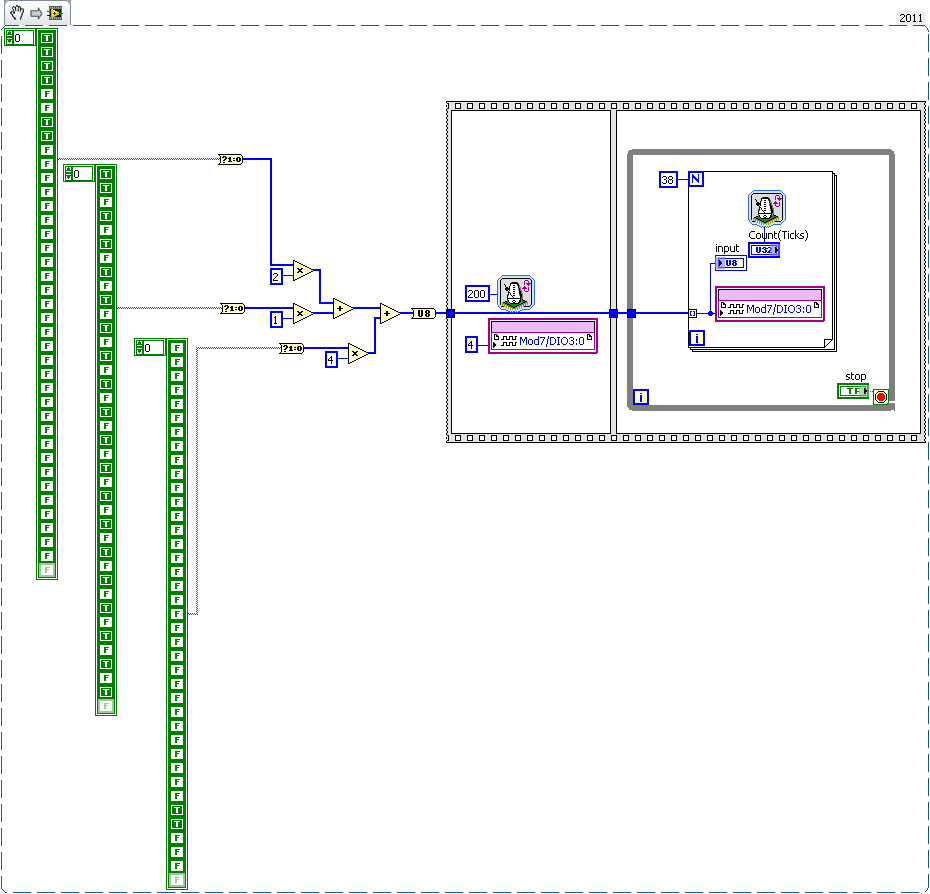

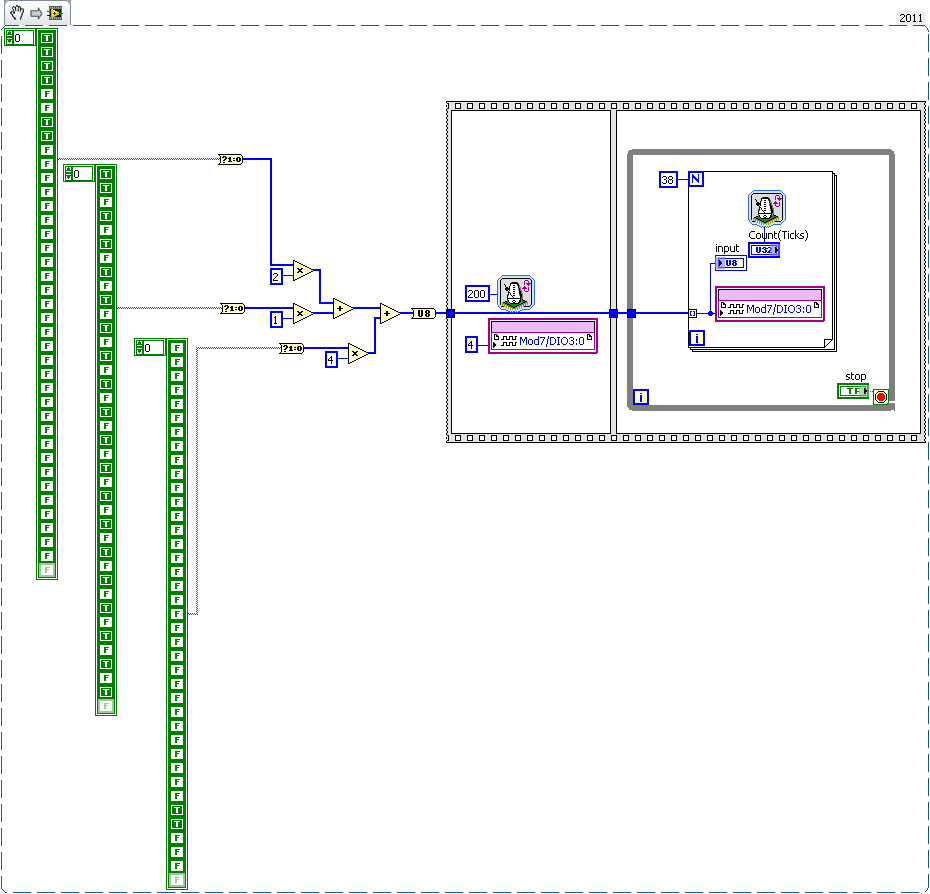

Da

es konfortabler ist einfach die Ausgänge direkt parallel zu setzen nutz

man am besten den Mod7/DIO3:0 FPGA I/O Node.

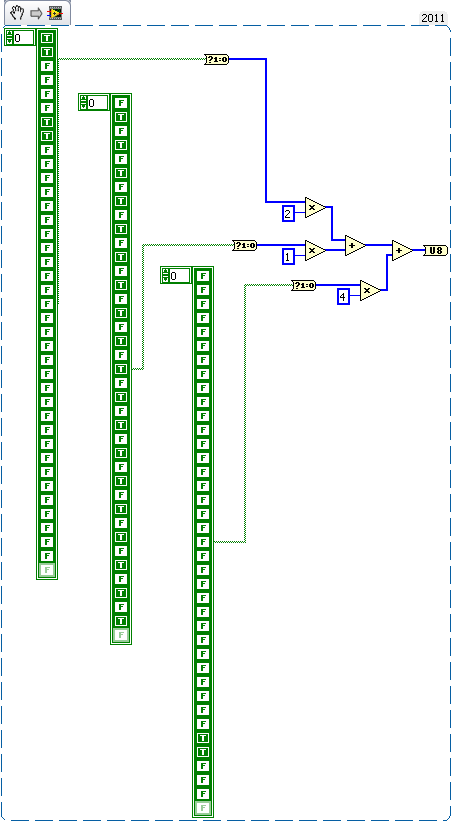

Nun

muss man noch die Binären Daten in Integerzahlen umwandeln.

DIO0 steht für 1, DIO1 steht für 2 und DIO2 steht für 4.

Der

Rest sollte sich von selbst erklären. In der Sequenz wird CS auf

High gesetzt, um dem MCP3002 zum erstenmal den Startvorgang zu

signalisieren. Über Count (Ticks) stellt man die f_CLK ein und

für einen Tick benötigt die cRio 25ns. f_CLK soll ca. 3,2 MHz

sein, der Kehrwert der Frequenz ergibt den Zeit Wert 312,5ns. Eine

Periode soll also 312,5 ns sein. Da man diesen Wert allerdings

nicht mit 25 ns erreicht nimmt man den nächst gelegen (z.B.

300ns). Rechnerisch muss man hier noch beachten, dass das Programm so

aufgebaut ist das der CLK Ausgang erst Low dann High geschaltet wird,

eine Periode hier aber aus Low und High besteht, somit ergibt sich

für Count (Ticks) der Wert 150 (ns).

Wenn

man das Programm soweit aufgebaut hat und DIO5 per Anzeige überwacht,

müsste man schon erste Ergebnisse beobachten können. Die

Verarbeitung des Signals ergibt sich wieder aus dem Diagramm FIGURE

5-1. Das IC antwortet sofort nachdem Din übergeben wurde mit einem

Null Bit, dann mit Bit 9, B8... B1 und B0. Klar ist hier (von

links nach rechts) B0 hat den Wert 1, B1 entspricht 2, B3 der 4,....,B8

dem Wert 256 und B9 ist gleich 512. Da der MCP3002 ein 10 Bit Wandler

ist steht dem Anwender eine Auflösung von

5V/1024=0,0048828125 V = 4,88mV zur Verfügung.

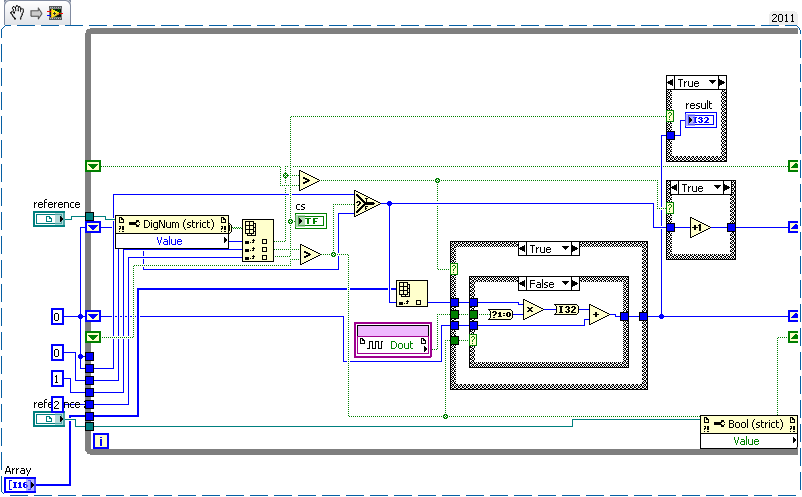

Die

Logik ist recht simpel, auch wenn der Programmausschnitt auf den ersten

Blick verwirrend aussieht. Den Bits 9 bis 0 von Dout sind die Zahlen aus

"Array" zugeordnet. Dies geschieht über CLK. Wenn die Logik die

untere Case-Struktur frei gibt geschieht die Zuweisung Bit9 bis Bit0

zu Zahlenwert 512 bis 1, dabei werden die Bits mit ihrem Faktor

multipliziert und anschließend addiert. Wird Din auf High

gesetzt, fängt das Programm erneut bei Bit9 (eigentlich beim NullBit)

an zu zählen. Die Auswertung von CS erneuert das "result" in der obersten

Case-Struktur, damit keine überflüssigen Ergebnisse weiter

gereicht werden. Was man nicht vergessen darf ist , dass der MCP3002

vor Bit9 ein Nullbit schickt, somit wartet man auf 11 Bits, wobei das

erste immer Low Pegel hat. Das Messergebniss muss natürlich noch

umgerechnet werden. (5V/1024)*Messwert = Spannungswert.

Sollte die Kommunikation nicht auf Anhieb klappen, die f_CLK verändern, den Kanalwechseln über Din (CH0/ CH1), Signalpegel und Anschlüsse überprüfen, die Pegel CLK verschieben oder die Pegel von Din out verändern. Hilfreich bei der Fehlersuche ist ein Oszilloskop. Welches den Anschluss Dout überwacht.

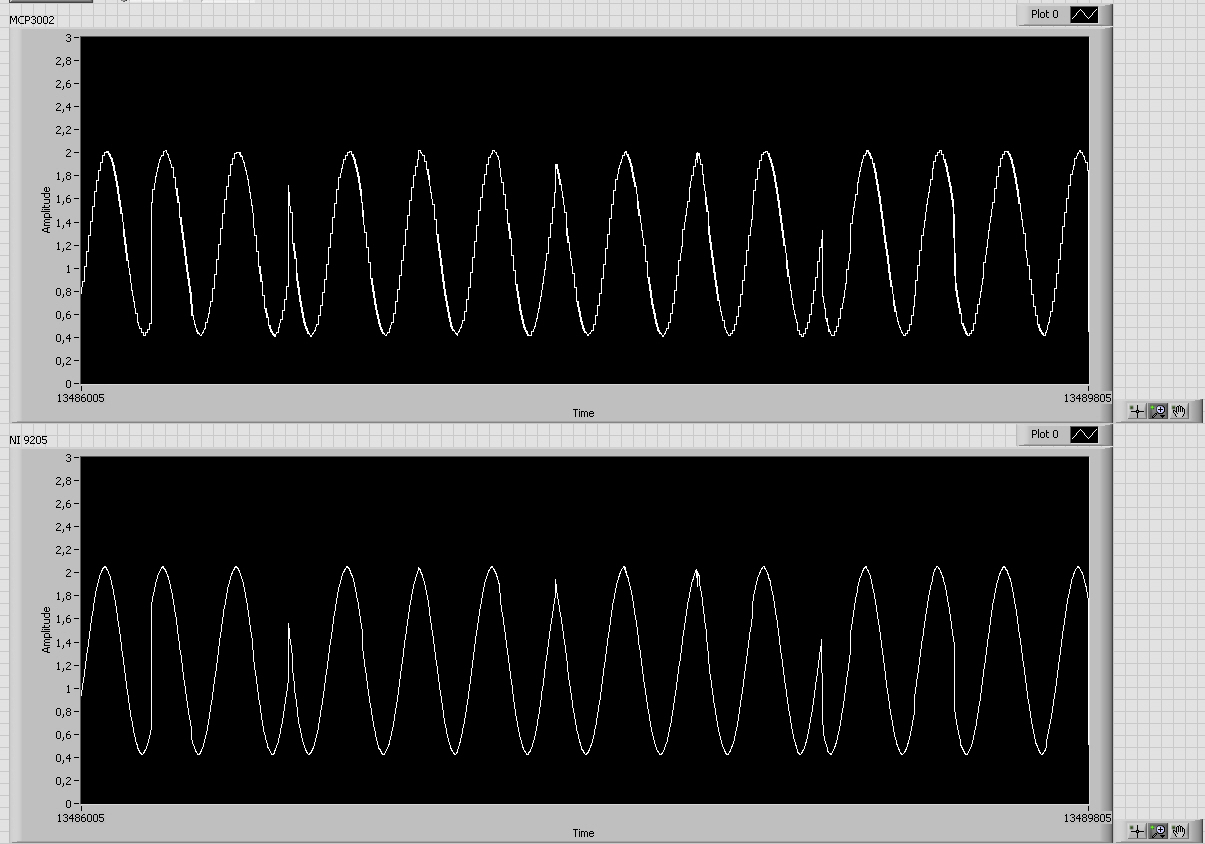

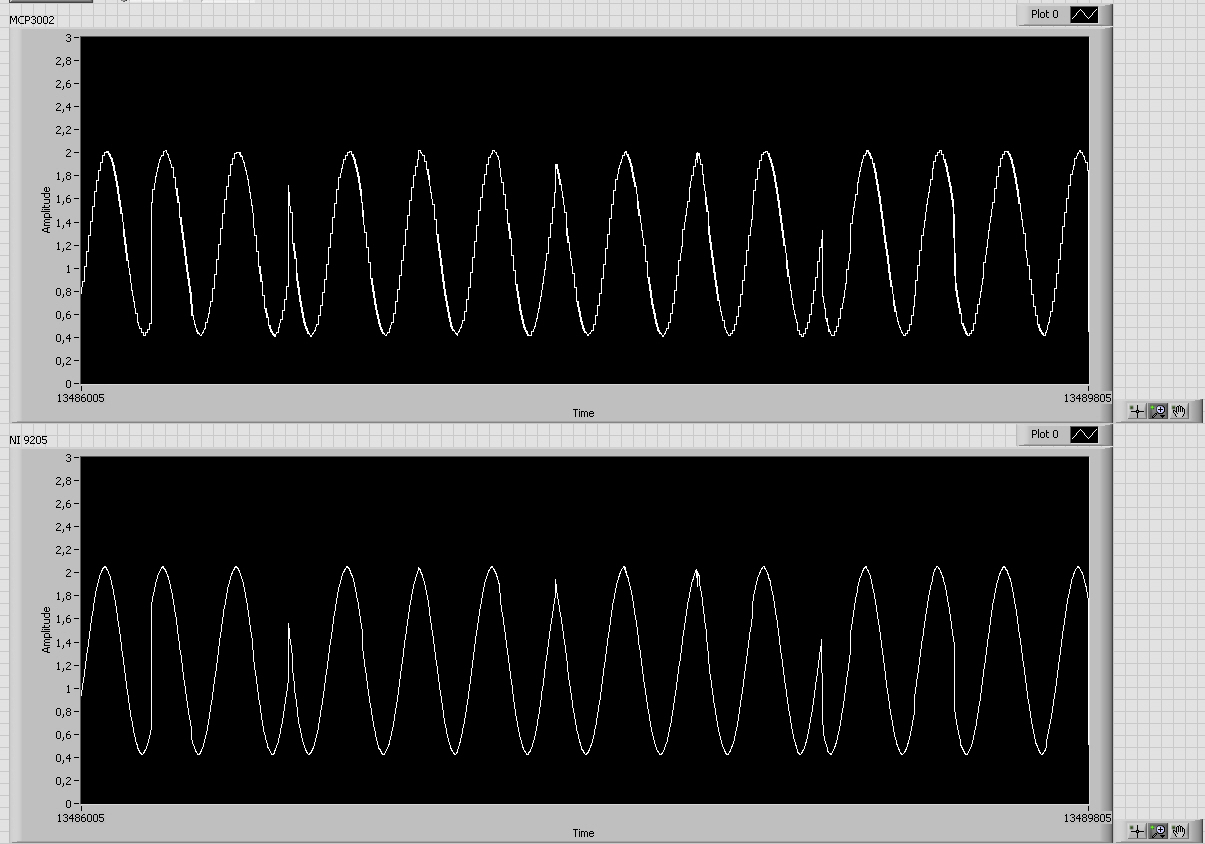

Hier noch ein Vergleich zwischen dem MCP3002 und dem Modul NI 9205.

Der MCP3002 bietet natürlich nur 10 Bit. Daher auch der Treppen-Signalverlauf, gegenüber dem Modul NI 9205 mit 16 Bit. Durch die Verschaltung und Programmierung des MCP3002 + FPGA VI, besteht leicht die Möglichkeit drei weitere MCP3002 anzuschließen, die die selben Steuersignale bekommen und einzeln jeweils einen Dout haben. Somit kann man 4 Analoge Eingänge mit einer Abtastrate von ca. 200 kHz oder durch Umschalten von Din 8 Analoge Eingänge mit einer Abtastrate von ca.100 kHz erstellen.

Sollte die Kommunikation nicht auf Anhieb klappen, die f_CLK verändern, den Kanalwechseln über Din (CH0/ CH1), Signalpegel und Anschlüsse überprüfen, die Pegel CLK verschieben oder die Pegel von Din out verändern. Hilfreich bei der Fehlersuche ist ein Oszilloskop. Welches den Anschluss Dout überwacht.

Hier noch ein Vergleich zwischen dem MCP3002 und dem Modul NI 9205.

Der MCP3002 bietet natürlich nur 10 Bit. Daher auch der Treppen-Signalverlauf, gegenüber dem Modul NI 9205 mit 16 Bit. Durch die Verschaltung und Programmierung des MCP3002 + FPGA VI, besteht leicht die Möglichkeit drei weitere MCP3002 anzuschließen, die die selben Steuersignale bekommen und einzeln jeweils einen Dout haben. Somit kann man 4 Analoge Eingänge mit einer Abtastrate von ca. 200 kHz oder durch Umschalten von Din 8 Analoge Eingänge mit einer Abtastrate von ca.100 kHz erstellen.